(IJAER) 2011, Vol. No. 2, Issue No.V, November

http://www.ijaer.com/

ISSN: 2231-5152

# DESIGN AND SIMULATION OF A TYPICAL HIGH PERFORMANCE AHB RECONFIGURABLE MASTER FOR ONCHIP BUS ARCHITECTURE USING VERILOG HDL

#### \*Rohit Hardia, #Prof.Jai Karan Singh, \$Prof..MukeshTiwari

Dept. of Electronics & Communication, SSSIST, SEHORE (M.P.)INDIA #Head of Department, Dept. of Electronics & Communication, SSSIST, SEHORE, INDIA \$Dean Academics, SSSIST, SEHORE, INDIA

# ABSTRACT

Resolution is a big issue in system on chip while dealing with number of masters trying to sense a single data bus. This paper presents the Design and Simulation of a typical High Performance AHB Reconfigurable Master for Onchip Bus Architecture using verilog HDL. In this methodology I here used wrap logic to generate data at specific time by several bus masters. The key point in this paper is wrap logic. The FSM for AHB master has been generated and simulated on modelsim HDL tool. The scheme involves several AMBA features of pipelined operation, multiple bus masters, burst transfers, split transations. The purpose of this paper is to propose a scheme to implement reconfigurable architectures so that it can be interfaced with any IP core as such a system using AMBA busspecification.

Here we proposed generation of AMBA ABH master using wrap logic. The design architecture is written using Verilog HDL using Modelsim tool. The timing diagrams are also generated on this tool. The synthesis of the design is done on Xilinx tool. The mapping, floorplaning, places and routes are also generated on Xilinx tool. **Keywords**-reconfigurable master, split transation, burst transfer, wrap logic, AMBA, AHB, Verilog HDL, Xilinx, FPGA.

# **INTRODUCTION TO AMBA**

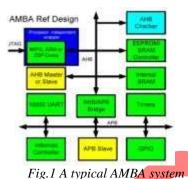

The Advanced Microcontroller Bus Architecture (AMBA) specification defines on chip communication standards for designing high-performance embeddedmicrocontrollers.

Three buses are defined in this specification:

- 1) the Advanced High Performance Bus(AHB)

- 2) the Advanced SystemBus(ASB)

- 3) the Advanced Peripheralbus(APB)

### **ADVANCED HIGH-PERFORMANCE BUS(AHB)**

This bus is used for high-performance, high clock frequency system modules. This bus is acts as the backbone bus. AHB efficiently interconnects processors, on-chip memories and off-chip external memories interfaces with low-power peripherals macrocell functions.

(IJAER) 2011, Vol. No. 2, Issue No.V, November

### ISSN: 2231-5152

### **AHB BUS SPECIFICATION**

AHB is a new generation of AMBA bus which is intended to address the requirements of highperformance synthesizable designs. AMBA AHB is a new level of bus which sits above the APB and implements the features required for high-performance, high clock frequency system including:

- A. bursttransfers

- B. splittransitions

- C. single cycle bus masterhandover

- D. single clock edgeoperation

- E. non-tristateimplementation

- F. Larger data bus configurations (64/128bits).

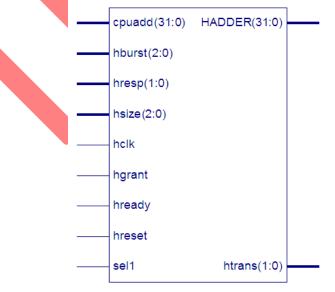

# AHB BUS MASTER INTERFACE

An AHB bus master has the most complex bus interface is an AMBA system. In this paper I implement this AMBA ABH master using wrap logic. Since there are several master can be used in AMBA specification so the arbiter can choose any one of that at the time of transfer. The interface diagram of ABH bus master shows the main signal groups.

### **International Journal of Advances in Engineering Research**

49

(IJAER) 2011, Vol. No. 2, Issue No.V, November

#### http://www.ijaer.com/

ISSN: 2231-5152

### DATA PATH

The ABH Master can be broken into sub systems. The two major components of the system under design are the controller and data path. The data path are further divided into several subsystems. All these subsystems are then controlled by the top module and a FSM module. Some of these data path are as follows-

- 1. **Control unit block:-**Different inputs from the arbiter like hready, hclk, hreset are using as inputs to this block.this block then generate a datadone signal asoutput.

- 2. Early burst generation and termination block:-There are several circumstances when a burst will not be allowed to complete and therefore it is important that any slave design which makes use of the burst information can take the correct course of action if the burst is terminated early. The slave can determine when a burst has terminated early by monitoring the HTRANS signals and ensuring that after the start of the burst every transfer is labeled as SEQUENTIAL or BUSY. If a NONSEQUENTIAL or IDLE transfer occurs then this indicates that a new burst has started and therefore the previous one must have been terminated. For example, if a master has only completed one beat of a four-beat burst then it must use an undefined-length burst to perform the remainingtransfers.

- 3. **Burst transfer block:-** A granted bus master starts an AMBA AHB transfer by driving the address and control signals. These signals provide information on the address, direction and width of the transfer, as well as an indication if the transfer forms part of a burst. Two different forms of burst transfers areallowed

- a) incrementing bursts, which do not wrap at addressbiundaries

- b) wrapping bursts, which wrap at particular addressboundaries.

- 4. Counter(4 bit)

- 5. Multiplexor( $2 \times 1$  and  $8 \times 1$ )

- 6. Adder (16bit)

# **DEVICE UTILIZATION SUMMARY**

| Selected device: xcv50-6fg256 |     |  |  |

|-------------------------------|-----|--|--|

| Number of Slices              | 124 |  |  |

| Number of Slice Flip Flops    | 66  |  |  |

| Number of 4 input LUTs        | 242 |  |  |

| Number of Bonded IOBs         | 76  |  |  |

|                               |     |  |  |

Table.1

Total equivalent gate count for design: 2970Total JTAG countfor IOBs: 3696

http://www.ijaer.com/

(IJAER) 2011, Vol. No. 2, Issue No.V, November

### ISSN: 2231-5152

# **RESULTS AND SIMULATION**

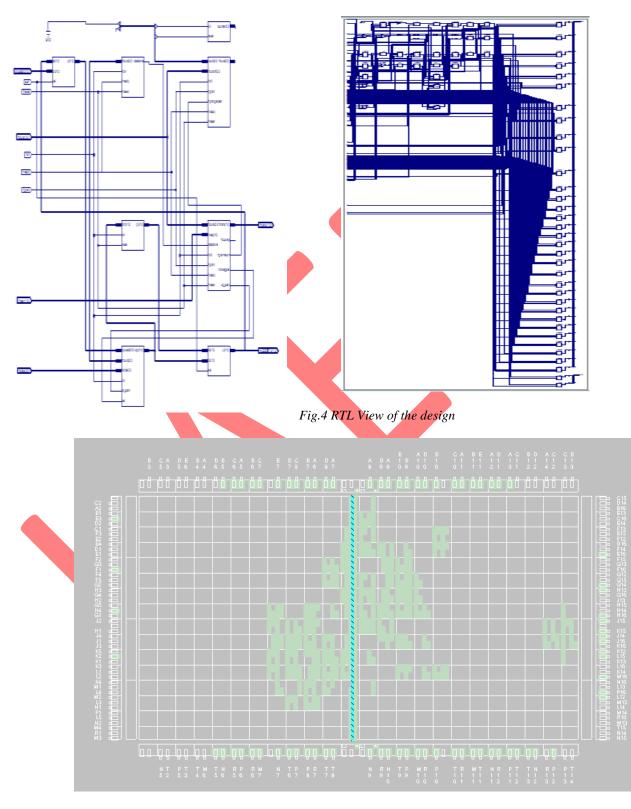

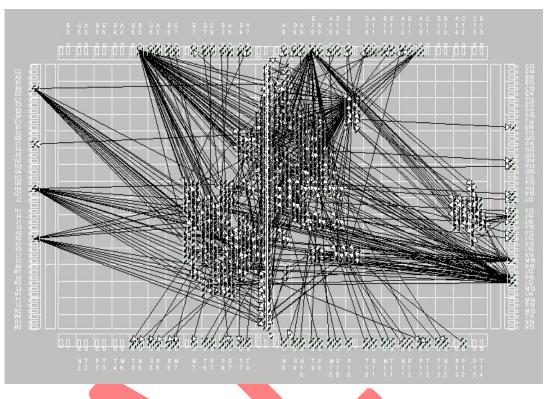

The design is simulated on modelsim. The advantage of this design is that we have taken care of area consumption hence with less latch and maximum flip-flops have enhanced our area efficiency. FSM coding has been done for controller design. The resulting simulation timing diagram, RTL view and Floorplan results are shown below:-

| _                 |                                                              |                |                            |  |

|-------------------|--------------------------------------------------------------|----------------|----------------------------|--|

| - 🎱 i             | /topm/clk                                                    |                |                            |  |

| - 🎱 i             | /topm/op_start                                               | Sti            |                            |  |

| . <u>⊕</u> -⊛     | /topm/cpuadd                                                 | 00000000000000 |                            |  |

| - <b>2</b> -      | /topm/sel                                                    | Sr1            |                            |  |

|                   | /topm/hsize                                                  | 001            |                            |  |

| œ- <b>⊘</b> /     | /topm/hburst                                                 | 101            |                            |  |

|                   | /topm/op                                                     |                |                            |  |

| . <u>⊕-</u> ⊘ /   | /topm/op1                                                    |                |                            |  |

|                   | /topm/op2                                                    |                |                            |  |

| ⊡- <b>⊘</b> /     | /topm/op3                                                    |                |                            |  |

|                   | /topm/op6                                                    |                |                            |  |

| ⊡- <b>2</b> /     | /topm/y0                                                     |                |                            |  |

| ⊡- <b>2</b> /     | /topm/y1                                                     |                |                            |  |

| ⊡- <b>2</b> /     | /topm/y2                                                     |                |                            |  |

|                   | /topm/y3                                                     |                |                            |  |

|                   | /topm/y4                                                     |                |                            |  |

| ⊡- <b>⊘</b> /     | /topm/y5                                                     |                |                            |  |

| . <u>⊕-</u> ⊘ /   | /topm/y6                                                     |                |                            |  |

| . <u>⊕</u> -⊘     | /topm/y7                                                     |                |                            |  |

| ⊡- <b>⊘</b> /     | /topm/M1/a                                                   |                |                            |  |

| ⊡- <b>⊘</b> /     | /topm/M1/b                                                   |                |                            |  |

| - 🥘 i             | /topm/M1/sel                                                 | Sr1            |                            |  |

| . <u>⊕-</u> ∂ /   | /topm/M1/y                                                   |                |                            |  |

| ، <del>آت</del> ے | /topm/M4/a                                                   |                | sim:/topm/N1/sel 0 1365 ns |  |

|                   | /topm/M4/b                                                   |                | St1                        |  |

| - 🥘 i             | /topm/M4/sel                                                 | Sri            |                            |  |

| ⊡- <b>⊘</b> /     | /topm/M4/y                                                   |                |                            |  |

| . <u>⊕</u> ⊸      | /topm/A/a                                                    |                |                            |  |

| ⊡- <b>⊘</b> /     | Лорт/А/Б                                                     |                |                            |  |

| 2                 | /topm/A/op_start                                             | Sr1            |                            |  |

| ⊡- <b>2</b> /     | /topm/A/sum                                                  |                |                            |  |

| ⊡- <b>2</b> /     | /topm/M2/sel                                                 | 001            |                            |  |

|                   | Fig. 3 Modelsim Simulation waveform of AHB Master top module |                |                            |  |

Fig.3 Modelsim Simulation waveform of AHB Master top module

http://www.ijaer.com/

### (IJAER) 2011, Vol. No. 2, Issue No.V, November

Fig.5 Floorplan of the design

International Journal of Advances in Engineering Research

52

http://www.ijaer.com/

(IJAER) 2011, Vol. No. 2, Issue No.V, November

#### ISSN: 2231-5152

Fig.6 Places and route on the device

### **REFERENCES**

[1] AMBA Specification Rev 2.0.ARM Ltd., 1999.<u>http://www.arm.com</u>

[2] Marc Bertola, Guy Bois " A Methodology for the design of AHB bus master wrappers" Groupe de recherché en microelectronique(GRM)

[3] A.K.Singh, Anurag Shrivastava, G.S.Tomar"Design and Implementation of High Performance Reconfigurable Arbiter for Onchip Bus Architecture." 2011 International Conference on communication System and NetworkTechnologies.

[4] IBM inc., The CoreConnect BusArchitecture

[5] Silicore inc., WISHBONE System-on-chip Interconnection architecture, 2001

[6] Zhang Qing-li, YU Ming-yan, Wang Jin-xiang, YE Yi-zheng, LAI Feng-chang.,"The Design of AMBA AHB/VCI Wrapper."Microelectronics Centre, Harbin, 150001, P.R.China

http://www.ijaer.com/

(IJAER) 2011, Vol. No. 2, Issue No.V, November

ISSN: 2231-5152

[7] Adeoye Olugbon, Aami Khawam, Tughrul Arslan, Ioannis Nousias, Iain Lindsay, "AN AMBA AHB-BASED RECONFIGURABLE SOC ARCHITECTURE USING MULTIPLICITY OF DEDICATED FLYBY DMA BLOCKS" School of Engineering and Electronics, The University of Edinburgh,Scotland

[8] Adeoye Olugbon, Tughrul Arslan, Iain Lindsay,"AFormal Approach to Virtualisation and Provisioning in AMBA ABH-based Reconfigurable System-on-chip."Schl, of Engr. & Electronics The University of Edinburgh Scotland,UnitedKingdom.

[9] Xilinx Inc., Using a Processor to Configure Xilinx FPGAs via Slave Serial or SelectMap mode:XAPP502(v1.4), Nov 2003.http://www.xilinx.com

[10] Ruibing Lu, Aiqun Cao, and Cheng-Kok Koh, Senior Member; IEEE,"SAMBA-Bus A High Performance Bus Architecture for System-on-Chip"IEEE Transactions on Very Large Scale Integration (VLSI) System, Vol.15,No. 1,January2007.

[11] IEEE Std.1364-1995 Verilog Language ReferenceManul